偦偙偱丄廃攇悢偺埨掕搙偼彮偟埆偔側傞偐傕偟傟傑偣傫偑丄VFO傪嶌傠偆偲巚偄傑偡丅

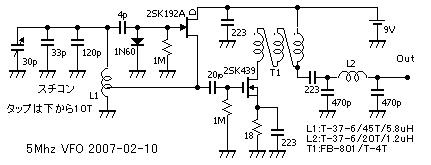

廃攇悢峔惉偼丄5.1乣5.4MHz偲偟偰丄15MHz偺悈徎傪3掽攞偟偨45MHz傪壛偊偰50.1乣50.4MHz偲偡傞梊掕偱偡丅

夞楬偼丄僜乕僗僞僢僾偺僴乕僩儗乕宆敪怳夞楬偱偡丅

乽僩儘僀僟儖僐傾妶梡昐壢乿傪嶲峫偵偟傑偟偨丅

嫟怳夞楬偺VC偲C偺慻傒崌傢偣偱廃攇悢壜曄斖埻傪寛掕偟傑偡丅

嵟戝廃攇悢傪Fmax丄嵟掅廃攇悢傪Fmin偲偡傞偲丄F=1/(2儺併(LC))偱偡偐傜丄埲壓偺娭學偑偁傝傑偡丅

丂丂丂丂VC/C=(Fmax/Fmin)^2-1

VC偵偼30pF偺FM梡偺PVC傪巊偄傑偡丅

VC偺嵟戝梕検偼岞徧抣傪怣偠傞偲偟偰丄嵟彫抣偼悢pF偁傞偼偢偱偡丅

傑偨丄晜梀梕検傕悢pF壛傢偭偰偄傑偡丅

幚嵺偼幚尡偟偰傒傞偺偑憗偄偺偱偡偑丄偙偙偱偼堦墳愝寁偟偰傒傑偡丅

Fmax=5.4MHz丄Fmin=5.1MHz丄VC=30pF偲偡傞偲C=248pF偲側傝傑偟偨丅

30pF傕壜曄斖埻偑偁傞偲偼巚偊傑偣傫偺偱丄VC=20pF偲偡傞偲丄C=165pF偱偡丅

偙偺斖埻偺拞偵惓夝偑偁傞偼偢偱偡丅

VC偺梕検傪惓妋偵應掕偟偰傒傟偽嶲峫偵側傝傑偡偑丄應掕忦審傗幚憰忬懺偵傛偭偰傇傟傑偡偺偱丄崱屻偺壽戣偲偟傑偡丅

崱夞偼丄C=165pF偐傜晜梀梕検10pF傪嵎偟堷偄偰155pF偱幚尡偟偰傒傑偡丅

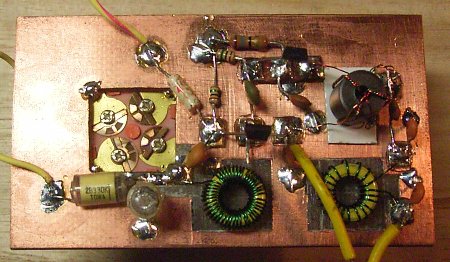

庤帩偪偺僗僠僐儞偺慻傒崌傢偣偱33+120pF偱偡丅

L偼C=165+20pF/F=5.1MHz偐傜L=5.26uH丅T-37-6僐傾(AL=3.0nH/t^2)傪巊偆偺偱丄N=併(L/AL)偐傜42T偲側傝傑偟偨丅

偙偺僷儔儊僞偱幚嵺偵夞楬傪慻傫偱應掕偟偰傒傑偟偨丅

F=5.6乣6.0MHz偲側傝丄C偑懌傝傑偣傫丅

庤帩偪偺僗僠僐儞偺娭學偱丄C偼偦偺傑傑偲偟偰丄L傪憹傗偟偰45T偲偟傑偟偨丅

VC偺僩儕儅傪挷惍偟偰丄5.095乣5.420MHz偲偟傑偟偨丅

偙偺夞楬恾偼悈嫑摪偝傫偺乽夞楬恾僄僨傿僞 BSch3V乿偱彂偒傑偟偨丅

悈嫑摪偝傫偁傝偑偲偆偛偞偄傑偟偨丅

偙偺偁偲僩儘僀僟儖僐傾偲僗僠僐儞傪僄億僉僔偱屌傔偰丄僾儕儞僩婎斅偱僔乕儖僪働乕僗傪嶌惉偟偰姰惉偺梊掕偱偡丅

弌椡偼9dBm偱偟偨丅

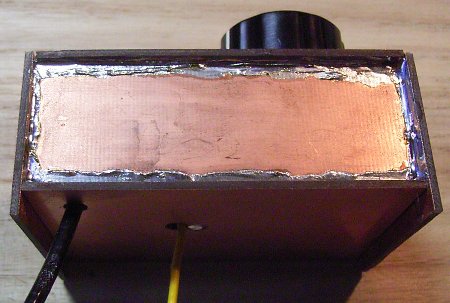

僾儕儞僩婎斅傪愗偭偰丄働乕僗傪嶌傝傑偡丅

惓妋偵愗傝弌偡偺偼戝曄偱偡丅

椉榚傪晅偗偨偲偙傠偱偡丅